1장 목차는 다음과 같습니다.

- 1.1 서론

- 1.2 컴퓨터 구조 분야의 일곱 가지 위대한 아이디어

- 1.3 프로그램 밑의 세계

- 1.4 케이스를 열고

- 1.5 프로세서와 메모리 생산 기술

- 1.6 성능

- 1.7 전력장벽

- 1.8 현저한 변화: 단일프로세서에서 멀티프로세서로의 변화

- 1.9 결론

- 1.10 오류 및 함정

서론 부분은 앞선 포스트에 상세히 적혀있으니, 생략하고, 1.2부터 정리하도록 하겠습니다.

1.2

컴퓨터 구조 분야의 일곱가지 위대한 아이디어

- 설계를 단순화 하는 추상화 -> 자원의 수가 증가함에 따라 생산성을 높이기 위한 기술 개발

- 자주 생기는 일을 빠르게

- 병렬성을 통한 성능 개선

- 파이프라이닝(명령어의 실행을 중첩시켜 프로그램을 빠르게 실행시키는 기술)을 통한 성능 개선

- 예측을 통한 성능 개선

- 메모리 계층 구조

- 여유분을 위한 신용도 개선

1.3

프로그램 밑의 세계

각 계층을 동심원으로 나타냈을 때, 하드웨어가 가장 중심에 있고 응용 소프트웨어가 가장 바깥쪽에 있게 됩니다.

- 응용 소프트웨어 : 상위 수준 언어(HLL)로 작성

- 시스템 소프트웨어

- 컴파일러 : HLL -> machine code

- 운영 체제(OS) : service code

- 인풋/아웃풋 관리

- 메모리와 저장공간 관리

- 스케줄링, 자원 관리

- 하드웨어

- 프로세서, 메모리, 입출력 컨트롤러

상위 수준 언어에서 기계어 까지

1. 프로그래머가 A+B와 같은 상위 수준 언어 수식 작성

2. 컴파일러가 이것을 번역해서 A+B를 add A, B와 같은 어셈블리 언어 문장으로 바꿈

3. 어셈블러가 A와 B를 더하라는 이진 명령어로 바꿈

1.4

케이스를 열고

컴퓨터의 고전적 다섯 가지 구성 요소 : 입력, 출력, 메모리, 데이터패스, 제어유닛

입출력장치 : 마이크, 키보드, 스피커, 무선 네트워크를 위한 장치

터치스크린 : PostPC시대의 태블릿, 스마트폰(키보드와 마우스의 역할)

프로세서(CPU) 내부

- 데이터패스 : 데이터 연산의 집합

- 제어 : 다양한 컴포넌트를 제어

- 캐시메모리 : 작고 빠른 메모리로서 데이터로 즉각적인 접근이 가능

- DRAM : 작고 빠른 메모리(캐시 메모리도 이에 속함)

- SRAM : DRAM보다 빠르지만, 집적도가 낮아서 가격이 비쌈(캐시)

데이터의 안전한 저장소

- 휘발성 메인 메모리 : 파워가 끊기면 모든 기억이 지워짐

- 비휘발성 보조기억장치 : 자가디스크, 플래시 메모리, 광학디스크

네트워크

- 통신, 자원공유, 원격공유

- 근거리 네트워크(LAN) : Ethernet

- 원거리 네트워크(WAN) : the Internet

- 무선 네트워크 : wifi, bluetooth

1.5

프로세서와 메모리 생산기술

트랜지스터 : 전기로 제어되는 on/off 스위치

집적회로의 집적도 증가 -> 용량 및 성능 증가, 비용 감소

반도체 기술

실리콘 : 반도체

화학적 처리를 거쳐 불순물을 첨가 :

전기의 양도체, 전기 절연체, 스위치

칩 생산 공정 과정

실리콘 괴를 자른 후 20 내지 40단계의 공정을 거쳐 빈 웨이퍼에 패턴이 새겨집니다. 패턴이 새겨진 웨어퍼를 웨이퍼 검사기로 검사해서 불량 부분에 표시를 합니다. 이 웨이퍼를 잘라서 다이를 만들고, 다이의 수율은 3개가 이상이 있으므로, 17/20 => 85%입니다. 검사를 통과한 다이는 패키지에 붙이고, 남품하기 전에 다시 검사를 합니다.

다이 : 웨이퍼에서 잘라낸 개개의 사각형, 칩이라고 부름

수율 : 웨이퍼상의 전체 다이 중 양호한 다이의 비율

성능

성능을 바라보는 관점은 속도적인 관점과 대역폭(=처리량)의 관점 두 가지가 있습니다.

응답 시간(Response time) : 태스크를 수행하는 데 걸리는 시간-> 응답 시간의 관점에서 실행 시간이 더욱 중요

처리량(Throughput) : 일정한 시간 동안 처리하는 작업의 양 -> 작업의 양이 중요

Performance = 1/Execution Time = 성능 = 1/실행시간

Performance(x) / Performance(y) == Execution time(y) / Execution time(x) = n

Performance(성능)와 Execution Time(실행 시간)은 역수 관계이다.

경과시간

- 한 작업을 끝내는데 필요한 전체 시간(프로세싱, I/O..)

- 시스템 성능 정의

CPU 실행시간

- 프로세서가 순수하게 처리한 시간

- 사용자 CPU 시간과 시스템 CPU 시간으로 나뉨

- 프로그램에 따라서 민감하게 영향받는 시간이 다름

CPU 클럭

모든 컴퓨터는 하드웨어 이벤트가 발생하는 시점을 결정하는 클럭을 이용하여 만들어짐

onstant-rate clock에 의해 하드웨어 작동(연속된 시간이 아닌, 이산화된 시간에 의해서 작동)

클럭 주기: 한 사이클에 걸린 시간

클럭 속도 : 1초에 실행되는 사이클 수

CPU 시간

성능 개선법 : 클럭 사이클 수를 늘리거나, 클럭 속도를 높임.

명령어 수와 CPI (명령어당 클럭 사이클 수)

프로그램 당 명령어 수, 명령어 당 클럭 사이클 수는 평균으로 계산(만약 CPI가 다르다면, 명령어 조합에 영향을 받음)

ex) Computer A : Cycle Time = 250ps, CPI = 2.0, Computer B : Cycle Time = 500ps, CPI = 1.2

CPU Time(A) = Instruction Count * CPI(A) * Cycle Time(A) = I * 2.0 * 250ps = I * 500ps

CPU Time(B) = Instruction Count * CPI(B) * Cycle Time(B) = I * 1.2 * 500ps = I * 600ps

CPU Time(B) / CPU Time(A) => A가 1.2배 더 빠릅니다.

if CPI가 다른 경우

클럭 사이클 수

CPI 계산

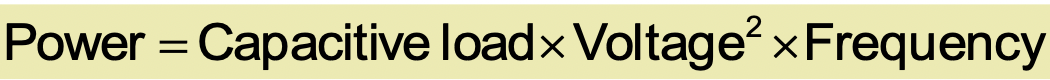

전력과 상대 전력

만약, 새로운 CPU가 기존 CPU에 비해 85%의 용량성 부하를 갖고, 15%의 전압, 15%의 빈도 감소를 갖는다면, 상대전력은 다음과 같습니다.

전력 장벽(전압을 더 낮출 수 없고, 열을 제거할 수 없음)

단일프로세서 성능

전력개선, 명령어 수준 병렬성, 메모리 개선으로 인해 성능 향상이 더 이상 크지 않음

멀티프로세서

멀티코어 프로세서

한 칩당 하나 이상의 프로세서

명시적 병렬 프로그램을 요구

명령어 수준 병렬성과의 비교

하드웨어가 한 번에 여러 개의 명령어들을 처리

프로그래머들에게 숨겨져 있음

어려운 이유

성능을 중시하기에 프로그래밍이 어려움, 코어 간 공평한 분배가 어려움

통신 및 동기화 오버헤드를 줄여야 함

'CS' 카테고리의 다른 글

| [컴퓨터 구조] chapter2-1 정리(컴퓨터 언어 : 명령어) (0) | 2023.04.11 |

|---|---|

| [HTTP] 개발자로서 갖춰야할 HTTP 지식 (0) | 2023.04.11 |

| [컴퓨터 구조] 컴퓨터 시스템의 구성 (0) | 2023.04.07 |

| [HTTP] Internet Network (0) | 2023.03.30 |

| [컴퓨터 구조] 컴퓨터의 혁명과 컴퓨터 종류 (0) | 2023.03.27 |